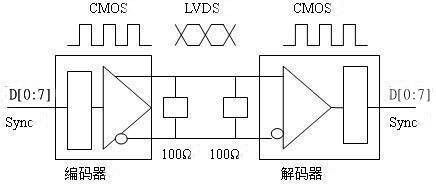

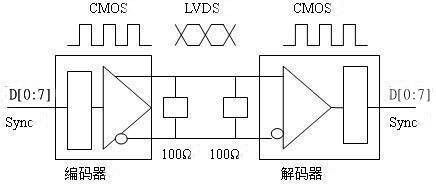

本系統的數據傳輸模式是點對點模式,由圖像獲取模塊的微型攝像模組獲取待檢活體視頻圖像信號傳送到圖像處理模塊,因此,采用 LVDS 技術的點對點拓撲結構,如圖 3.6 所示。

圖 3.8 LVDS 編碼電路

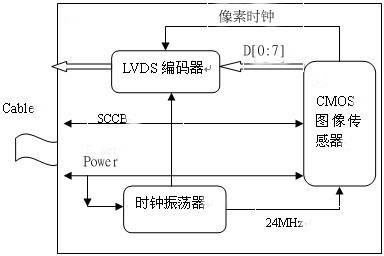

本系統的 CMOS 圖像傳感器輸出的是 30fps、分辨率為1280 ′1024 和 8 位的并行數字視頻圖像信號,視頻圖像信號有同步信號 VSYNC、HREF,像素時鐘信號 PCLK 和視頻信號 D[0:9],將同步信號、像素信號以及高 8 位視頻信號輸入到 LVDS 編碼芯片,編碼生成 LVDS 串行信號,圖像傳輸模塊的前端如圖3.7 所示。

圖 3.8 LVDS 編碼電路

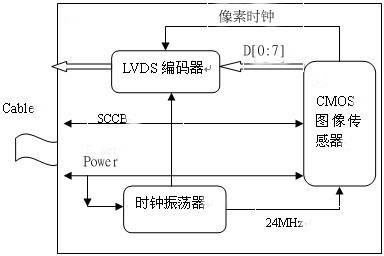

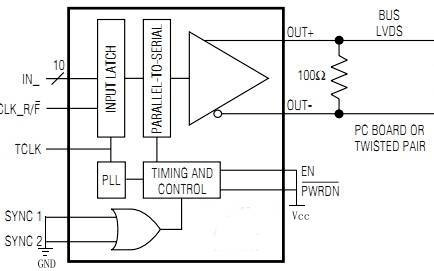

本文應用Maxim 公司生產的 10 位串行器/編碼器 MAX9205 和并行器/解碼器 MAX9206 實現對傳輸信號的串并轉換。

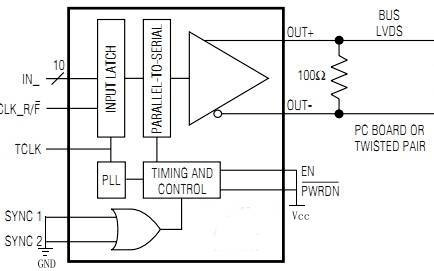

LVDS 編碼器將 10 位的并行 LVCMOS/LVTTL 信號轉換為串行總線低壓差分信號數據流,編碼器的經典應用一般都要配合解碼器,解碼電路將在后續章節介紹。本系統使用的 LVDS 編碼器能夠轉換串行數據以高達 400Mbps 和660Mbps 分別在 PCB 銅質導線和雙絞線上傳輸。編碼器無需外圍部件和控制信號,為了使編碼器工作在數據傳輸模式,兩個 SYNC 引腳要設置為低電平,PWRND 和 EN 必須設置為高電平。芯片的系統時鐘為 16MHz-40MHz,如果TCLK=40MHz,那么串行率為 480MHz,大于 CMOS 傳感器的視頻數據寬度,滿足系統設計要求,LVDS 編碼電路如圖 3.8 所示。

圖 3.8 LVDS 編碼電路

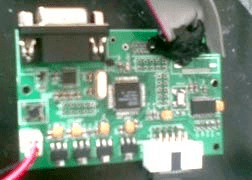

CMOS 圖像傳感器的同步信號和并行視頻圖像信號按照從高位到地位一次連接至編碼芯片的輸入引腳 IN[9:0],像素時鐘為圖像傳感器 PCLK 引腳連接到編碼芯片的系統時鐘 TCLK 引腳,像素時鐘為編碼器的系統時鐘,編碼器的數據高串行率是實現 LVDS 信號高速傳輸的基礎,LVDS 信號經過雙絞線傳送到解碼器解碼,然后傳送到圖像處理模塊。LVDS 編解碼電路實物圖如圖 3.9 所示

圖 3.9 LVDS 編解碼電路實物圖

產品咨詢

產品咨詢